উচ্চ-ক্ষমতার স্পন্দিত লেজারসম্পূর্ণ ফাইবার MOPA কাঠামো সহ

ফাইবার লেজারের প্রধান কাঠামোগত প্রকারগুলোর মধ্যে রয়েছে একক রেজোনেটর, বিম কম্বিনেশন এবং মাস্টার ওসিলেটিং পাওয়ার অ্যামপ্লিফায়ার (MOPA) কাঠামো। এদের মধ্যে, উচ্চ-কর্মক্ষমতা অর্জনের ক্ষমতার কারণে MOPA কাঠামোটি বর্তমান গবেষণার অন্যতম প্রধান কেন্দ্রবিন্দুতে পরিণত হয়েছে।স্পন্দিত লেজারসামঞ্জস্যযোগ্য পালস প্রস্থ এবং পুনরাবৃত্তি কম্পাঙ্ক সহ আউটপুট (যা পালস প্রস্থ এবং পুনরাবৃত্তি কম্পাঙ্ক হিসাবে উল্লেখ করা হয়)।

MOPA লেজারের কার্যপ্রণালী নিম্নরূপ: প্রধান অসিলেটর (MO) হলো একটি উচ্চ-ক্ষমতাসম্পন্ন সীড সোর্স।সেমিকন্ডাক্টর লেজারযা সরাসরি পালস মডুলেশনের মাধ্যমে সামঞ্জস্যযোগ্য প্যারামিটারসহ সীড সিগন্যাল লাইট তৈরি করে। ফিল্ড প্রোগ্রামেবল গেট অ্যারে (FPGA) প্রধান কন্ট্রোল সামঞ্জস্যযোগ্য প্যারামিটারসহ পালস কারেন্ট সিগন্যাল আউটপুট করে, যা ড্রাইভ সার্কিট দ্বারা নিয়ন্ত্রিত হয়ে সীড সোর্সকে পরিচালনা করে এবং সীড লাইটের প্রাথমিক মডুলেশন সম্পন্ন করে। FPGA প্রধান কন্ট্রোল বোর্ড থেকে নিয়ন্ত্রণের নির্দেশাবলী পাওয়ার পর, পাম্প সোর্স ড্রাইভ সার্কিট পাম্প লাইট তৈরি করার জন্য পাম্প সোর্সকে চালু করে। সীড লাইট এবং পাম্প লাইট বিম স্প্লিটারের মাধ্যমে সংযুক্ত হওয়ার পর, সেগুলোকে যথাক্রমে দ্বি-স্তরীয় অপটিক্যাল অ্যামপ্লিফিকেশন মডিউলের Yb3+-ডোপড ডাবল-ক্ল্যাড অপটিক্যাল ফাইবারে (YDDCF) প্রবেশ করানো হয়। এই প্রক্রিয়ার সময়, Yb3+ আয়নগুলো পাম্প লাইটের শক্তি শোষণ করে একটি পপুলেশন ইনভার্সন ডিস্ট্রিবিউশন তৈরি করে। পরবর্তীতে, ট্রাভেলিং ওয়েভ অ্যামপ্লিফিকেশন এবং স্টিমুলেটেড এমিশনের নীতির উপর ভিত্তি করে, সীড সিগন্যাল লাইট দ্বি-স্তরীয় অপটিক্যাল অ্যামপ্লিফিকেশন মডিউলে উচ্চ পাওয়ার গেইন অর্জন করে এবং অবশেষে একটি উচ্চ-ক্ষমতার আউটপুট প্রদান করে।ন্যানোসেকেন্ড পালসড লেজারসর্বোচ্চ শক্তি বৃদ্ধির কারণে, গেইন ক্ল্যাম্পিং প্রভাবের ফলে বিবর্ধিত পালস সিগন্যালের পালস প্রস্থ সংকুচিত হতে পারে। বাস্তব প্রয়োগে, আউটপুট শক্তি এবং গেইন দক্ষতা আরও বাড়ানোর জন্য প্রায়শই বহু-স্তরীয় বিবর্ধন কাঠামো গ্রহণ করা হয়।

MOPA লেজার সার্কিট সিস্টেমটি একটি FPGA প্রধান কন্ট্রোল বোর্ড, একটি পাম্প সোর্স, একটি সিড সোর্স, একটি ড্রাইভার সার্কিট বোর্ড, একটি অ্যামপ্লিফায়ার ইত্যাদি দ্বারা গঠিত। FPGA প্রধান কন্ট্রোল বোর্ডটি সামঞ্জস্যযোগ্য ওয়েভফর্ম, পালস প্রস্থ (৫ থেকে ২০০ ন্যানোসেকেন্ড) এবং পুনরাবৃত্তির হার (৩০ থেকে ৯০০ কিলোহার্টজ) সহ পালস বৈদ্যুতিক সংকেত তৈরি করে সিড সোর্সকে চালনা করে, যার ফলে সামঞ্জস্যযোগ্য প্যারামিটারসহ মেগাওয়াট-স্তরের কাঁচা সিড লাইট পালস নির্গত হয়। এই সংকেতটি আইসোলেটরের মাধ্যমে প্রি-অ্যামপ্লিফায়ার এবং প্রধান অ্যামপ্লিফায়ার দ্বারা গঠিত দ্বি-স্তরীয় অপটিক্যাল অ্যামপ্লিফিকেশন মডিউলে ইনপুট করা হয় এবং অবশেষে কলিমেশন ফাংশনসহ অপটিক্যাল আইসোলেটরের মাধ্যমে উচ্চ-শক্তির স্বল্প-পালস লেজার নির্গত করে। সিড সোর্সটিতে একটি অভ্যন্তরীণ ফটোডিটেক্টর রয়েছে যা রিয়েল টাইমে আউটপুট শক্তি পর্যবেক্ষণ করে এবং তা FPGA প্রধান কন্ট্রোল বোর্ডে ফিডব্যাক হিসেবে পাঠায়। প্রধান কন্ট্রোল বোর্ডটি পাম্প সোর্স ১, ২ এবং ৩-এর চালু ও বন্ধ করার কার্যক্রম সম্পন্ন করার জন্য পাম্প ড্রাইভ সার্কিট ১ এবং ২ নিয়ন্ত্রণ করে।ফটোডিটেক্টরসিগন্যাল লাইটের আউটপুট শনাক্ত করতে ব্যর্থ হলে, সীড লাইটের ইনপুটের অভাবে YDDCF এবং অপটিক্যাল ডিভাইসগুলোর ক্ষতি রোধ করার জন্য প্রধান কন্ট্রোল বোর্ড পাম্পের উৎস বন্ধ করে দেবে।

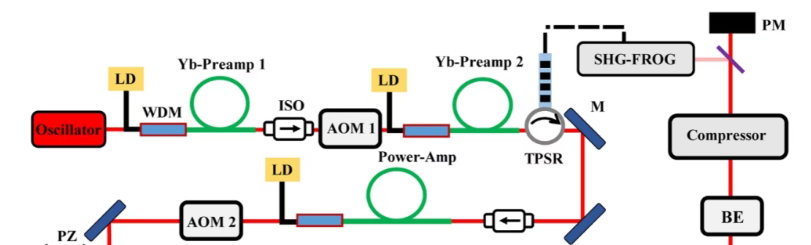

MOPA লেজার অপটিক্যাল পাথ সিস্টেমটি একটি সম্পূর্ণ ফাইবার কাঠামো গ্রহণ করে এবং এটি একটি প্রধান অসিলেশন মডিউল ও একটি দ্বি-পর্যায়ের অ্যামপ্লিফিকেশন মডিউল নিয়ে গঠিত। প্রধান অসিলেশন মডিউলটি সীড সোর্স হিসেবে ১০৬৪nm কেন্দ্রীয় তরঙ্গদৈর্ঘ্য, ৩nm লাইনউইডথ এবং ৪০০mW সর্বোচ্চ অবিচ্ছিন্ন আউটপুট পাওয়ার সম্পন্ন একটি সেমিকন্ডাক্টর লেজার ডায়োড (LD) ব্যবহার করে এবং এটিকে ৯৯%@১০৬৩.৯৪nm প্রতিফলন ক্ষমতা ও ৩.৫nm লাইনউইডথ সম্পন্ন একটি ফাইবার ব্র্যাগ গ্রেটিং (FBG)-এর সাথে সংযুক্ত করে একটি তরঙ্গদৈর্ঘ্য নির্বাচন সিস্টেম তৈরি করে। দ্বি-পর্যায়ের অ্যামপ্লিফিকেশন মডিউলটি একটি রিভার্স পাম্প ডিজাইন গ্রহণ করে এবং গেইন মিডিয়া হিসেবে যথাক্রমে ৮ ও ৩০μm কোর ব্যাসের YDDCF কনফিগার করা হয়। এর সংশ্লিষ্ট কোটিং পাম্প অ্যাবজর্পশন কো-এফিসিয়েন্ট হলো যথাক্রমে ১.০ এবং ২.১dB/m@৯১৫nm।

পোস্ট করার সময়: ১৭-সেপ্টেম্বর-২০২৫