উচ্চ-ক্ষমতাসম্পন্ন পালসড লেজারসম্পূর্ণ ফাইবার MOPA কাঠামো সহ

ফাইবার লেজারের প্রধান কাঠামোগত ধরণগুলির মধ্যে রয়েছে একক অনুরণনকারী, বিম সংমিশ্রণ এবং মাস্টার অসিলেটিং পাওয়ার এমপ্লিফায়ার (MOPA) কাঠামো। এর মধ্যে, উচ্চ-কর্মক্ষমতা অর্জনের ক্ষমতার কারণে MOPA কাঠামো বর্তমান গবেষণার অন্যতম কেন্দ্রবিন্দুতে পরিণত হয়েছে।স্পন্দিত লেজারসামঞ্জস্যযোগ্য পালস প্রস্থ এবং পুনরাবৃত্তি ফ্রিকোয়েন্সি সহ আউটপুট (যাকে পালস প্রস্থ এবং পুনরাবৃত্তি ফ্রিকোয়েন্সি বলা হয়)।

MOPA লেজারের কাজের নীতি নিম্নরূপ: প্রধান অসিলেটর (MO) হল একটি উচ্চ-কার্যক্ষমতাসম্পন্ন বীজ উৎসসেমিকন্ডাক্টর লেজারযা ডাইরেক্ট পালস মড্যুলেশনের মাধ্যমে অ্যাডজাস্টেবল প্যারামিটার সহ বীজ সংকেত আলো তৈরি করে। ফিল্ড প্রোগ্রামেবল গেট অ্যারে (FPGA) প্রধান নিয়ন্ত্রণ সামঞ্জস্যযোগ্য প্যারামিটার সহ পালস কারেন্ট সংকেত আউটপুট করে, যা ড্রাইভ সার্কিট দ্বারা নিয়ন্ত্রিত হয় বীজ উৎস পরিচালনা করার জন্য এবং বীজ আলোর প্রাথমিক মড্যুলেশন সম্পূর্ণ করার জন্য। FPGA প্রধান নিয়ন্ত্রণ বোর্ড থেকে নিয়ন্ত্রণ নির্দেশাবলী পাওয়ার পর, পাম্প উৎস ড্রাইভ সার্কিট পাম্প আলো তৈরি করতে পাম্প উৎস শুরু করে। বীজ আলো এবং পাম্প আলো বিম স্প্লিটার দ্বারা সংযুক্ত হওয়ার পরে, এগুলি যথাক্রমে দুই-পর্যায়ের অপটিক্যাল অ্যামপ্লিফিকেশন মডিউলে Yb3+ -ডোপড ডাবল-ক্ল্যাড অপটিক্যাল ফাইবার (YDDCF) ইনজেক্ট করা হয়। এই প্রক্রিয়া চলাকালীন, Yb3+ আয়নগুলি জনসংখ্যা বিপরীত বিতরণ তৈরি করতে পাম্প আলোর শক্তি শোষণ করে। পরবর্তীকালে, ভ্রমণ তরঙ্গ পরিবর্ধন এবং উদ্দীপিত নির্গমনের নীতির উপর ভিত্তি করে, বীজ সংকেত আলো দুই-পর্যায়ের অপটিক্যাল অ্যামপ্লিফিকেশন মডিউলে উচ্চ শক্তি লাভ অর্জন করে, অবশেষে একটি উচ্চ-শক্তি আউটপুট করেন্যানোসেকেন্ড পালসড লেজার। সর্বোচ্চ শক্তি বৃদ্ধির কারণে, গেইন ক্ল্যাম্পিং প্রভাবের কারণে অ্যামপ্লিফাইড পালস সিগন্যাল পালস প্রস্থ সংকোচনের সম্মুখীন হতে পারে। ব্যবহারিক প্রয়োগে, আউটপুট শক্তি আরও উন্নত করতে এবং দক্ষতা অর্জনের জন্য প্রায়শই মাল্টি-স্টেজ অ্যামপ্লিফিকেশন কাঠামো গ্রহণ করা হয়।

MOPA লেজার সার্কিট সিস্টেমটি একটি FPGA প্রধান নিয়ন্ত্রণ বোর্ড, একটি পাম্প উৎস, একটি বীজ উৎস, একটি ড্রাইভার সার্কিট বোর্ড, একটি পরিবর্ধক ইত্যাদির সমন্বয়ে গঠিত। FPGA প্রধান নিয়ন্ত্রণ বোর্ড বীজ উৎসকে MW-স্তরের কাঁচা বীজ আলোর পালস আউটপুট করতে চালিত করে, সামঞ্জস্যযোগ্য তরঙ্গরূপ, পালস প্রস্থ (5 থেকে 200ns) এবং পুনরাবৃত্তি হার (30 থেকে 900kHz) সহ পালস বৈদ্যুতিক সংকেত তৈরি করে। এই সংকেতটি আইসোলেটরের মাধ্যমে প্রি-অ্যামপ্লিফায়ার এবং প্রধান পরিবর্ধক দ্বারা গঠিত দ্বি-স্তরের অপটিক্যাল পরিবর্ধন মডিউলে ইনপুট করা হয় এবং অবশেষে কোলিমেশন ফাংশন সহ অপটিক্যাল আইসোলেটরের মাধ্যমে উচ্চ-শক্তির শর্ট-পালস লেজার আউটপুট করে। বীজ উৎসটি একটি অভ্যন্তরীণ ফটোডিটেক্টর দিয়ে সজ্জিত যা রিয়েল টাইমে আউটপুট শক্তি পর্যবেক্ষণ করে এবং FPGA প্রধান নিয়ন্ত্রণ বোর্ডে ফিরিয়ে আনে। প্রধান নিয়ন্ত্রণ বোর্ড পাম্প উৎস 1, 2 এবং 3 এর খোলার এবং বন্ধ করার ক্রিয়াকলাপ অর্জনের জন্য পাম্প ড্রাইভ সার্কিট 1 এবং 2 নিয়ন্ত্রণ করে। যখনফটোডিটেক্টরসিগন্যাল লাইট আউটপুট সনাক্ত করতে ব্যর্থ হলে, সিড লাইট ইনপুটের অভাবের কারণে YDDCF এবং অপটিক্যাল ডিভাইসগুলির ক্ষতি রোধ করতে প্রধান নিয়ন্ত্রণ বোর্ড পাম্প উৎসটি বন্ধ করে দেবে।

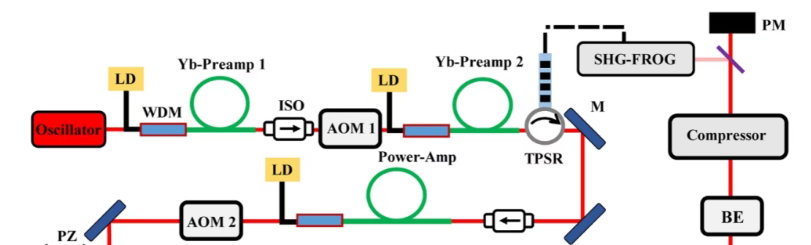

MOPA লেজার অপটিক্যাল পাথ সিস্টেমটি একটি সম্পূর্ণ ফাইবার কাঠামো গ্রহণ করে এবং এতে একটি প্রধান দোলন মডিউল এবং একটি দুই-স্তরের পরিবর্ধন মডিউল থাকে। প্রধান দোলন মডিউলটি একটি সেমিকন্ডাক্টর লেজার ডায়োড (LD) গ্রহণ করে যার কেন্দ্রীয় তরঙ্গদৈর্ঘ্য 1064nm, একটি লাইনউইথ 3nm এবং সর্বাধিক 400mW এর ক্রমাগত আউটপুট শক্তি বীজ উৎস হিসাবে ব্যবহার করে এবং এটিকে 99%@1063.94nm প্রতিফলন এবং 3.5nm এর লাইনউইথ সহ একটি ফাইবার ব্র্যাগ গ্রেটিং (FBG) এর সাথে একত্রিত করে একটি তরঙ্গদৈর্ঘ্য নির্বাচন ব্যবস্থা তৈরি করে। 2-স্তরের পরিবর্ধন মডিউলটি একটি বিপরীত পাম্প নকশা গ্রহণ করে এবং 8 এবং 30μm এর মূল ব্যাস সহ YDDCF যথাক্রমে লাভ মিডিয়া হিসাবে কনফিগার করা হয়। সংশ্লিষ্ট আবরণ পাম্প শোষণ সহগ যথাক্রমে 1.0 এবং 2.1dB/m@915nm।

পোস্টের সময়: সেপ্টেম্বর-১৭-২০২৫