ব্যবহার করেঅপটোইলেকট্রনিকবিপুল পরিমাণ ডেটা স্থানান্তরের সমস্যা সমাধানের জন্য কো-প্যাকেজিং প্রযুক্তি

কম্পিউটিং ক্ষমতার উচ্চতর স্তরে উন্নয়নের ফলে ডেটার পরিমাণ দ্রুত বৃদ্ধি পাচ্ছে, বিশেষ করে এআই লার্জ মডেল এবং মেশিন লার্নিং-এর মতো নতুন ডেটা সেন্টার বিজনেস ট্র্যাফিক এন্ড-টু-এন্ড এবং ব্যবহারকারীদের কাছে ডেটার বৃদ্ধিকে ত্বরান্বিত করছে। বিপুল পরিমাণ ডেটা দ্রুত সব দিকে স্থানান্তর করা প্রয়োজন, এবং ক্রমবর্ধমান কম্পিউটিং ক্ষমতা ও ডেটা ইন্টারঅ্যাকশনের চাহিদা মেটাতে ডেটা ট্রান্সমিশন রেটও 100GbE থেকে 400GbE, এমনকি 800GbE-তে উন্নীত হয়েছে। লাইন রেট বাড়ার সাথে সাথে সংশ্লিষ্ট হার্ডওয়্যারের বোর্ড-স্তরের জটিলতা ব্যাপকভাবে বৃদ্ধি পেয়েছে, এবং প্রচলিত I/O, ASics থেকে ফ্রন্ট প্যানেলে উচ্চ-গতির সিগন্যাল প্রেরণের বিভিন্ন চাহিদা মেটাতে অক্ষম হয়ে পড়েছে। এই প্রেক্ষাপটে, CPO অপটোইলেকট্রনিক কো-প্যাকেজিংয়ের চাহিদা বাড়ছে।

ডেটা প্রসেসিংয়ের চাহিদা বৃদ্ধি, সিপিওঅপটোইলেকট্রনিকসহ-সিল মনোযোগ

অপটিক্যাল কমিউনিকেশন সিস্টেমে, অপটিক্যাল মডিউল এবং AISC (নেটওয়ার্ক সুইচিং চিপ) আলাদাভাবে প্যাকেজ করা হয়, এবংঅপটিক্যাল মডিউলসুইচের সামনের প্যানেলে প্লাগেবল মোডে এটি সংযুক্ত করা হয়। প্লাগেবল মোড কোনো অপরিচিত বিষয় নয়, এবং অনেক প্রচলিত I/O সংযোগ এই মোডেই একসাথে যুক্ত করা হয়। যদিও প্রযুক্তিগত দিক থেকে প্লাগেবল এখনও প্রথম পছন্দ, উচ্চ ডেটা রেটে এই মোড কিছু সমস্যা প্রকাশ করেছে। ডেটা প্রসেসিং গতি আরও বাড়ানোর প্রয়োজন হলে অপটিক্যাল ডিভাইস এবং সার্কিট বোর্ডের মধ্যে সংযোগের দৈর্ঘ্য, সিগন্যাল ট্রান্সমিশন লস, বিদ্যুৎ খরচ এবং গুণমান সীমিত হয়ে পড়ে।

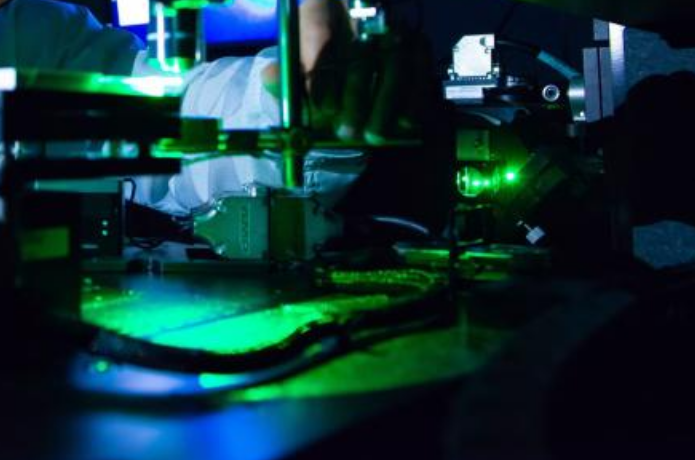

প্রচলিত সংযোগের সীমাবদ্ধতাগুলো সমাধান করার লক্ষ্যে, সিপিও অপটোইলেকট্রনিক কো-প্যাকেজিং মনোযোগ আকর্ষণ করতে শুরু করেছে। কো-প্যাকেজড অপটিক্সে, অপটিক্যাল মডিউল এবং এআইএসসি (নেটওয়ার্ক সুইচিং চিপ) একসাথে প্যাকেজ করা হয় এবং স্বল্প-দূরত্বের বৈদ্যুতিক সংযোগের মাধ্যমে সংযুক্ত করা হয়, যার ফলে কম্প্যাক্ট অপটোইলেকট্রনিক ইন্টিগ্রেশন অর্জন করা যায়। সিপিও ফটোইলেকট্রিক কো-প্যাকেজিংয়ের ফলে আকার এবং ওজনের সুবিধাগুলো সুস্পষ্ট, এবং এর মাধ্যমে উচ্চ-গতির অপটিক্যাল মডিউলগুলোর ক্ষুদ্রাকরণ সম্ভব হয়। অপটিক্যাল মডিউল এবং এআইএসসি (নেটওয়ার্ক সুইচিং চিপ) বোর্ডে আরও কেন্দ্রীভূত থাকে এবং ফাইবারের দৈর্ঘ্য ব্যাপকভাবে কমানো যায়, যার ফলে ট্রান্সমিশনের সময় লস বা ক্ষতি হ্রাস পায়।

আয়ার ল্যাবসের পরীক্ষার তথ্য অনুসারে, প্লাগেবল অপটিক্যাল মডিউলের তুলনায় সিপিও অপ্টো-কো-প্যাকেজিং সরাসরি বিদ্যুৎ খরচ অর্ধেক পর্যন্ত কমাতে পারে। ব্রডকমের হিসাব অনুযায়ী, ৪০০জি প্লাগেবল অপটিক্যাল মডিউলে সিপিও স্কিম প্রায় ৫০% বিদ্যুৎ সাশ্রয় করতে পারে এবং ১৬০০জি প্লাগেবল অপটিক্যাল মডিউলের তুলনায় সিপিও স্কিম আরও বেশি বিদ্যুৎ সাশ্রয় করে। আরও কেন্দ্রীভূত বিন্যাস আন্তঃসংযোগের ঘনত্বও ব্যাপকভাবে বাড়িয়ে দেয়, বৈদ্যুতিক সংকেতের বিলম্ব এবং বিকৃতি উন্নত হয় এবং প্রচলিত প্লাগেবল মোডের মতো ট্রান্সমিশন গতির সীমাবদ্ধতা আর থাকে না।

আরেকটি বিষয় হলো খরচ। আজকের কৃত্রিম বুদ্ধিমত্তা, সার্ভার এবং সুইচ সিস্টেমের জন্য অত্যন্ত উচ্চ ঘনত্ব এবং গতির প্রয়োজন, যার বর্তমান চাহিদা দ্রুত বাড়ছে। সিপিও কো-প্যাকেজিং ব্যবহার না করলে, অপটিক্যাল মডিউল সংযোগ করার জন্য প্রচুর সংখ্যক উচ্চমানের কানেক্টরের প্রয়োজন হয়, যা একটি বিশাল খরচের কারণ। সিপিও কো-প্যাকেজিং কানেক্টরের সংখ্যা কমাতে পারে, যা বিল অফ মেটেরিয়ালস (BOM) কমানোর ক্ষেত্রেও একটি বড় ভূমিকা রাখে। উচ্চ গতি, উচ্চ ব্যান্ডউইথ এবং কম শক্তির নেটওয়ার্ক অর্জনের একমাত্র উপায় হলো সিপিও ফটোইলেকট্রিক কো-প্যাকেজিং। সিলিকন ফটোইলেকট্রিক উপাদান এবং ইলেকট্রনিক উপাদানগুলোকে একসাথে প্যাকেজ করার এই প্রযুক্তি অপটিক্যাল মডিউলকে নেটওয়ার্ক সুইচ চিপের যতটা সম্ভব কাছাকাছি নিয়ে আসে, যা চ্যানেল লস এবং ইম্পিডেন্সের অসামঞ্জস্যতা কমায়, আন্তঃসংযোগের ঘনত্বকে ব্যাপকভাবে উন্নত করে এবং ভবিষ্যতে উচ্চ হারের ডেটা সংযোগের জন্য প্রযুক্তিগত সহায়তা প্রদান করে।

পোস্ট করার সময়: ০১-এপ্রিল-২০২৪